PIC2WS2812

Grundlagen

Die PIC Lösung

Software

Defines

Lösung

mit einem (kleinen) PIC

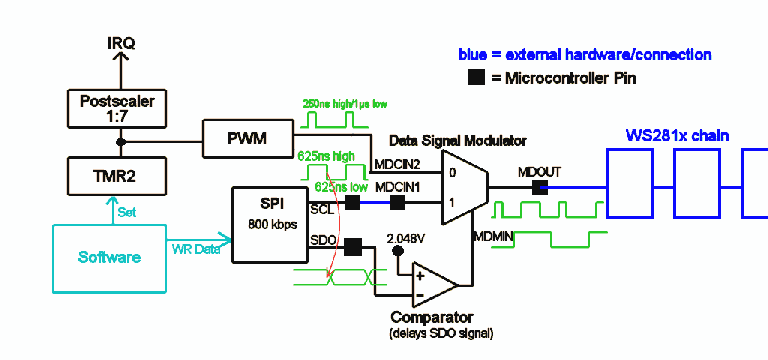

Im WWW findet man diverse Lösungen zur Ansteuerung von WS2812 LEDs mit Mikrocontrollern, meist auf Basis von Atmel-Mikrocontrollern/Arduino. Fast immer wird Bit-Banging für die Erzeugung des WS2812-Datensignals benutzt. Diese Lösung hat prinzipiell einen Nachteil: der Controller ist während der Datenausgabe zu 100% ausgelastet und kann in dieser Zeit nichts anderes tun, als vorab gespeicherte LED-Daten an die LEDs zu schicken. Für eine Berechnung von Lichtmustern ist daher auch die maximale Anzahl der LEDs durch die Größe des zur Verfügung stehenden RAMs begrenzt, denn das komplette Datenpaket muss ja vor der Übertragung erst im Speicher zusammengebaut werden. Außerdem kann der Controller während der Übertragung nicht auf Ereignisse von außen reagieren, wie z.B. Datenempfang auf einer seriellen Schnittstelle. Es gibt von Microchip eine Application Note (AN1606) für PIC16F1509, wo das Signal mit Hilfe der Confiigurable Logic Cell (CLC) und dem MSSP-Modul (als SPI-Schnittstelle) erzeugt wird und so die Notwendigkeit des Bit-Bangings umgangen wird. Dieser Lösungsansatz ließ mich über eine alternative Lösung für einen kleineren Controller (ohne CLC) nachdenken. Die Motivation dafür war nicht, eine fertige Lösung für meine (ohnehin nicht vorhandene) WS2812-Anwendung zu finden, sondern auszutüfteln, was man mit den beschränkten Hardware-Resourcen des in der Bastelkiste vorhandenen PIC12F1840 anstellen kann...

Die Herausforderung:

- Erzeugung des Datensignals mit Timing entsprechend der Spezifikation lt. Datenblatt

- unter Verwendung von ausschließlich "onboard"-Hardware des PIC12F1840 (keine weiteren, externen Bauteile)

- keine Beschränkung der LED-Anzahl durch RAM-Größe

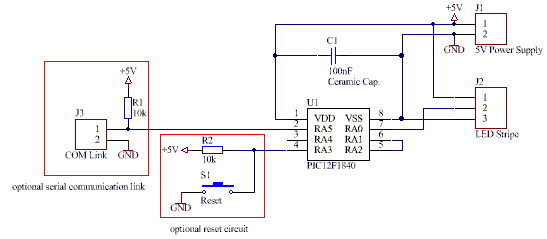

Und hier der Schaltplan:

Funktionsweise:

Wenn ein Byte fertig übertragen wurde, muss die Software rechtzeitig eingreifen, denn die sonst weiterlaufende PWM-Logik würde weitere Impulse erzeugen. Daher wird schon vor der Ausgabe des letzten Bits, bereits beim vorletzten (= 7.) PWM-Impuls, über den Postscaler von TMR2 ein Interrupt ausgelöst, durch den rechtzeitig die Ausgabe des nächsten Datenbytes oder das kontrollierte Ende der Datenübertragung veranlasst wird. Nur so ist auch die zügige Ausgabe der Daten, ohne unnötig große Lücken zwischen den Datenbytes, möglich.

Dennoch muss hier ein kleiner Abstrich bei der Übertragungsrate gegenüber der "idealen" Datenrate von 800 Kbit/s (= 10 µs/Byte) hingenommen werden! Das SPI Senderegister des PIC ist nicht gepuffert und erlaubt das Schreiben des nächsten Datenbytes erst, nachdem das letzte Datenbyte vollständig ausgegeben wurde. Hierdurch ergibt sich ein kleiner "Overhead" von 0,5µs zwischen zwei Bytes, so daß effektiv alle 10,5 µs ein Byte gesendet wird.

Weiter geht's mit der Software.